您好,登錄后才能下訂單哦!

您好,登錄后才能下訂單哦!

這篇文章主要介紹了FPGA卡拉ok系統中i2s輸入輸出的示例分析,具有一定借鑒價值,感興趣的朋友可以參考下,希望大家閱讀完這篇文章之后大有收獲,下面讓小編帶著大家一起了解一下。

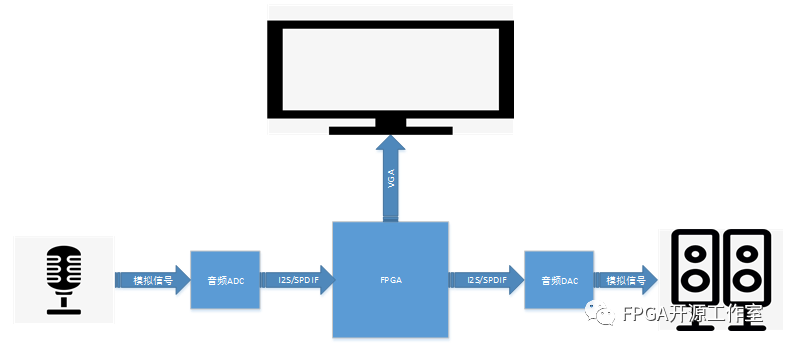

1 硬件需求介紹

圖1 卡拉ok硬件系統

1)麥克風(microphone)

2)音頻ADC --PCM1080或其他音頻ADC

3)FPGA --卡拉ok系統

4)音頻DAC--PCM5102A

5)音響

6)顯示屏

2 音頻ADC DAC介紹

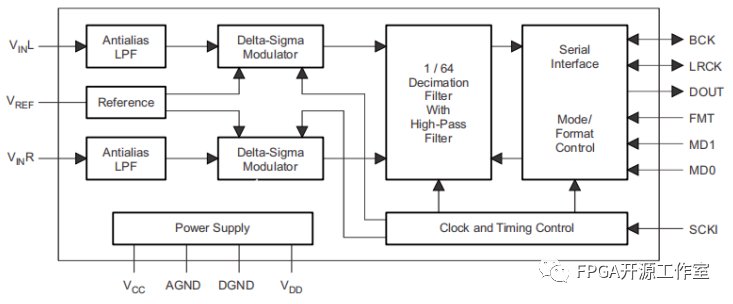

1) 音頻adc--pcm1080

PCM1808單端,模擬輸入24位,96kHz立體聲ADC。

性能:

– THD + N:–93 dB(典型值)

– SNR:99 dB(典型值)

–動態范圍:99 dB(典型值)

過采樣抽取濾波器:

–過采樣頻率:×64

–通帶紋波:±0.05 dB

–阻帶衰減:–65 dB

–片上高通濾波器:0.91 Hz(48 kHz)

PCM音頻接口:

–主模式或從模式可選

–數據格式:24位I2S,24位左對齊

采樣率:8 kHz–96 kHz

圖2 PCM1080 框圖

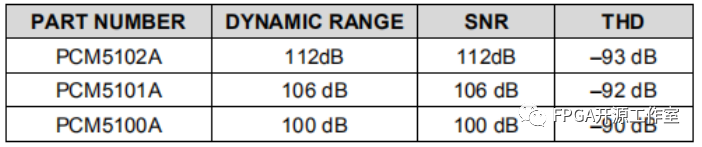

2)音頻dac--PCM5102a:

PCM510xA 2.1 VRMS,112/106/100 dB音頻立體聲DAC具有PLL和32位384 kHz PCM接口。

PCM510xA 的動態范圍、SNR以及THD的表現:

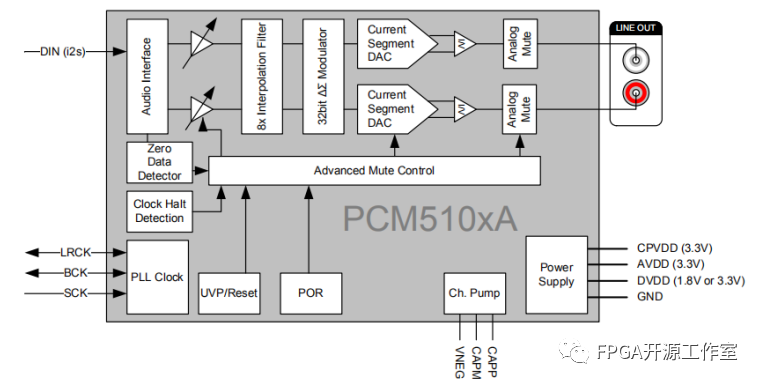

圖3 PCM5102A框圖

3 FPGA硬件系統介紹

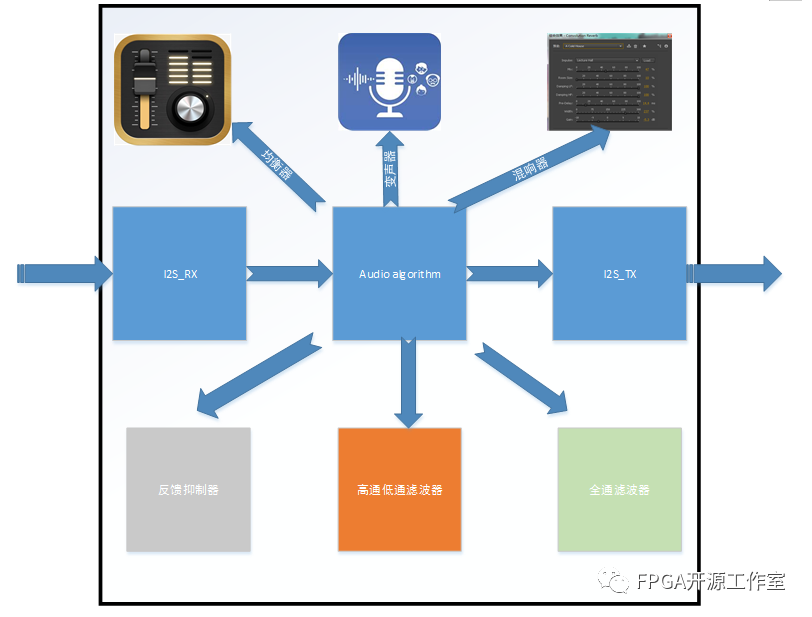

圖4 fpga內部音頻算法系統

音頻模擬信號經過音頻adc采集后轉化為數字信號通過I2S送入FPGA,FPGA內部可做均衡器算法,反饋抑制算法,高低通濾波器混響回聲以及變聲的音頻處理算法。

4 i2s的接收與發送

1)i2s概述

I2S(Inter—IC Sound)總線, 又稱 集成電路內置音頻總線,是飛利浦公司為數字音頻設備之間的音頻數據傳輸而制定的一種總線標準,該總線專門用于音頻設備之間的數據傳輸,廣泛應用于各種多媒體系統。I2S采用了沿獨立的導線傳輸時鐘與數據信號的設計,通過將數據和時鐘信號分離,避免了因時差誘發的失真,為用戶節省了購買抵抗音頻抖動的專業設備的費用。

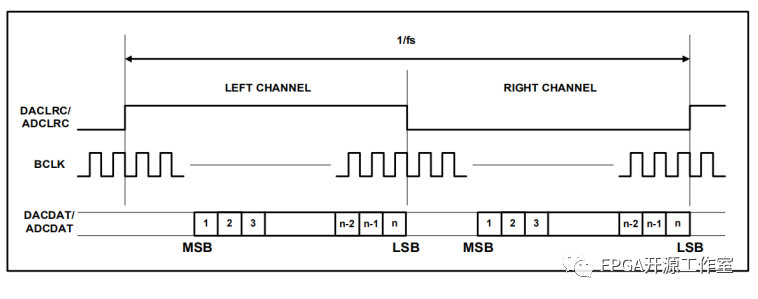

在飛利浦公司的I2S標準中,I2S主要有三個信號。

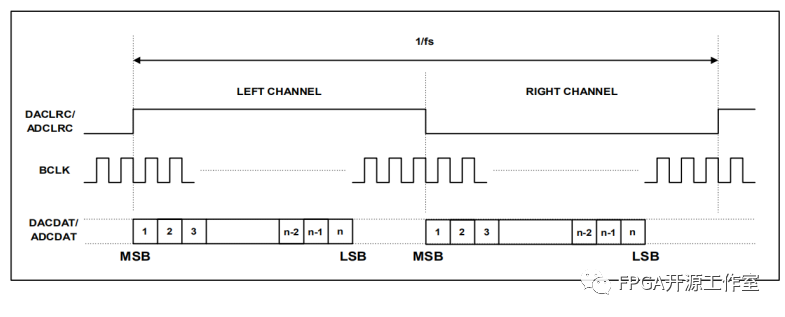

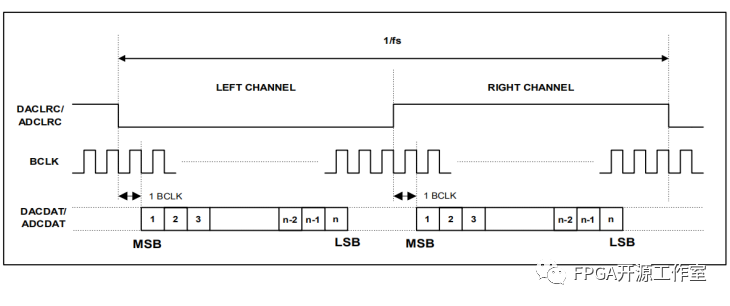

1.位時鐘 BICK(也叫串行時鐘SCLK),即對應數字音頻的每一位數據,BCLK都有1個脈沖。BCLK的頻率=2×采樣頻率×采樣位數。

2.幀時鐘LRCK,(也稱WS),用于切換左右聲道的數據。LRCK為“1”表示正在傳輸的是右聲道的數據,為“0”則表示正在傳輸的是左聲道的數據。LRCK的頻率等于采樣頻率。

3.串行數據SDATA,就是用二進制補碼表示的音頻數據。

有時為了使系統間能夠更好地同步,還需要另外傳輸一個信號MCLK,稱為主時鐘,也叫系統時鐘(Sys Clock),是采樣頻率的256倍或384倍。隨著技術的發展,在統一的 I2S接口下,出現了多種不同的數據格式。根據SDATA數據相對于LRCK和SCLK的位置不同,分為左對齊(較少使用)、I2S格式(即飛利浦規定的格式)和右對齊(也叫日本格式、普通格式)。

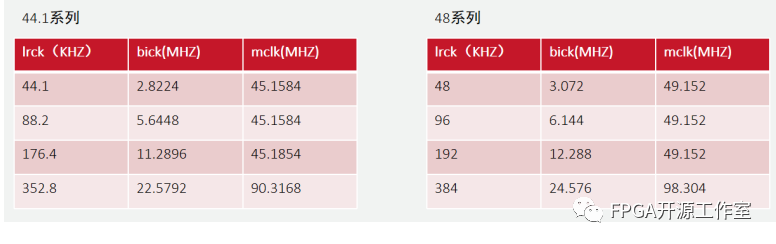

以下是I2S Sample rate 44.1Khz 和48Khz部分系列。

2) 模式

左對齊模式:SDATA 的MSB在BCLK的第一個上升獲得根據LRCK的傳輸。

I2S模式:SDATA 的MSB在BCLK的第二個上升獲得根據LRCK的傳輸。

右對齊模式。

感謝你能夠認真閱讀完這篇文章,希望小編分享的“FPGA卡拉ok系統中i2s輸入輸出的示例分析”這篇文章對大家有幫助,同時也希望大家多多支持億速云,關注億速云行業資訊頻道,更多相關知識等著你來學習!

免責聲明:本站發布的內容(圖片、視頻和文字)以原創、轉載和分享為主,文章觀點不代表本網站立場,如果涉及侵權請聯系站長郵箱:is@yisu.com進行舉報,并提供相關證據,一經查實,將立刻刪除涉嫌侵權內容。