您好,登錄后才能下訂單哦!

您好,登錄后才能下訂單哦!

本篇內容介紹了“FPGA中Retiming原理是什么”的有關知識,在實際案例的操作過程中,不少人都會遇到這樣的困境,接下來就讓小編帶領大家學習一下如何處理這些情況吧!希望大家仔細閱讀,能夠學有所成!

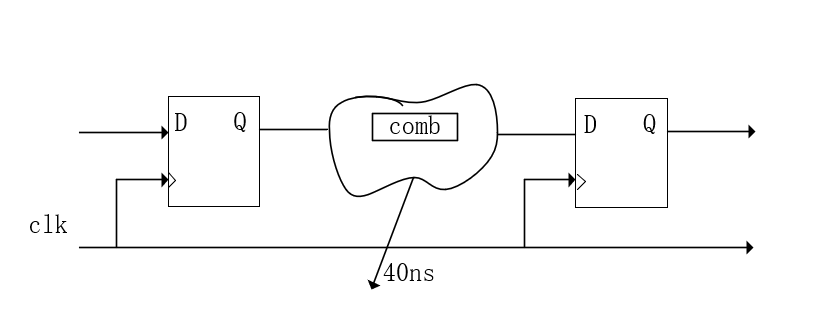

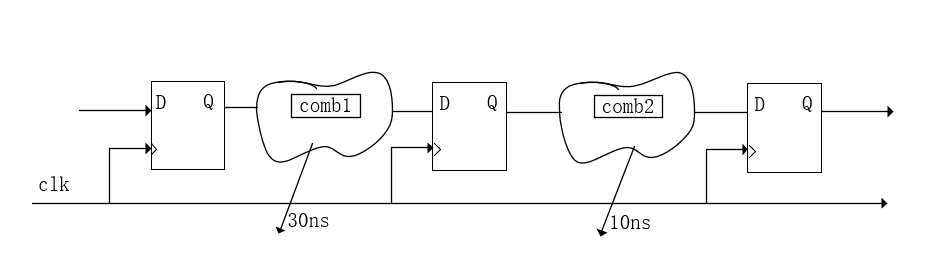

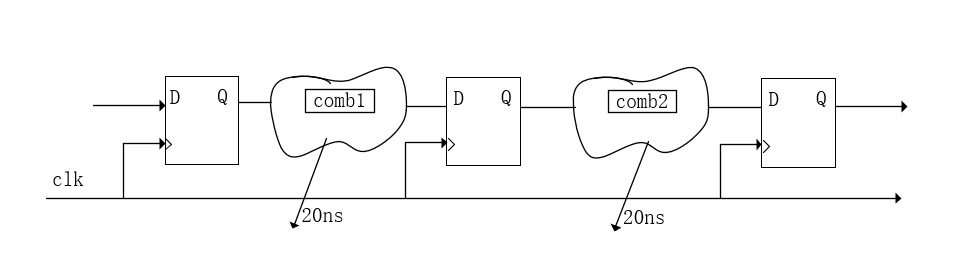

重定時(Retiming)是一種時序優化技術,用在不影響電路輸入/輸出行為的情況下跨組合邏輯寄存器從而提高設計性能。

Retiming就是重新調整時序,例如電路中遇到復雜的組合邏輯,延遲過大,電路時序不滿足,這個時候采用流水線技術,在組合邏輯中插入寄存器加流水線,進行操作,面積換速度思想。

我們知道任何的數字電路都可以等效成組合邏輯加D觸發器打拍,兩個D觸發器之間的組合邏輯路徑決定了,系統的工作頻率,決定芯片的性能。所以為了提高芯片的工作頻率,使用流水線技術在組合邏輯中插入寄存器。

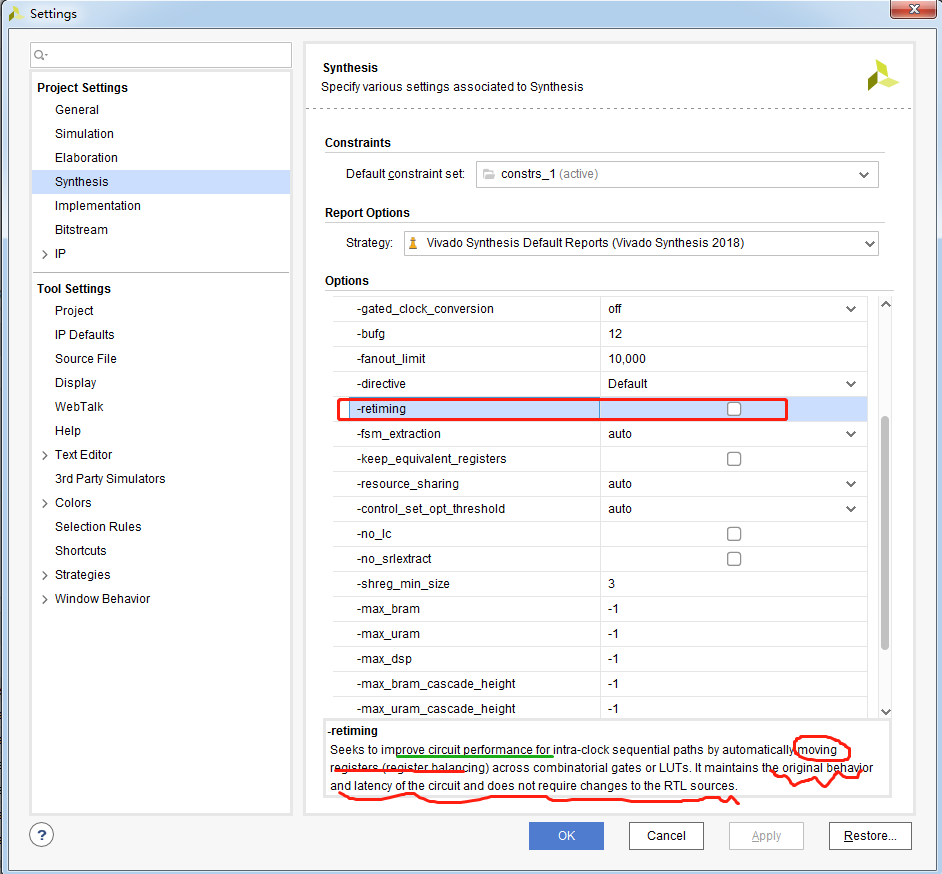

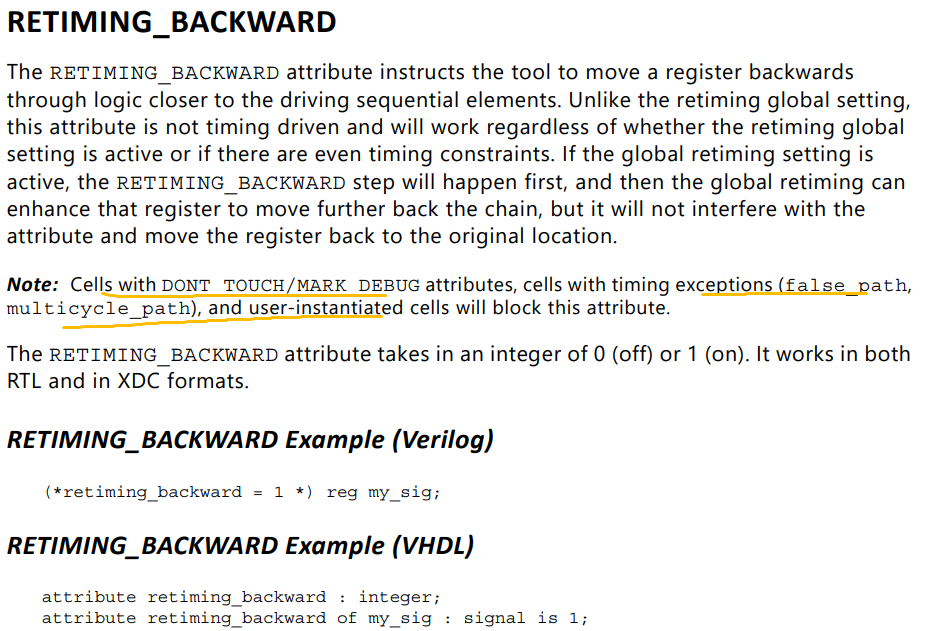

在Vivado 綜合操作中有兩種方法實現自動重定時(全局定時器),全局重定時是對整個設計而言的,基于設計時的時序要求優化大型組合邏輯結構中的寄存器設計。

這種方式需要分析設計中的所有邏輯,優化最壞路徑情況下的寄存器從而使整體設計反應速度更快。為了實現這一點設計時必須在.xdc文件中規定準確的時間限制。在synth_design或Vivado GUI綜合設置下通過-retiming命令啟用全局重定時,此外該特性還可以與合成中的BLOCK_SYNTH特性一起用于設計中的特定模塊。

寄存器時序異常(多循環路徑、錯誤的路徑、最大延遲路徑)

寄存器的類型屬性不能改變(DONT_TOUCH, MARK_DEBUG)

采用不同控制級的寄存器

“FPGA中Retiming原理是什么”的內容就介紹到這里了,感謝大家的閱讀。如果想了解更多行業相關的知識可以關注億速云網站,小編將為大家輸出更多高質量的實用文章!

免責聲明:本站發布的內容(圖片、視頻和文字)以原創、轉載和分享為主,文章觀點不代表本網站立場,如果涉及侵權請聯系站長郵箱:is@yisu.com進行舉報,并提供相關證據,一經查實,將立刻刪除涉嫌侵權內容。